| Chisel Lang | 624 Members |

| Discussion about the Chisel Hardware Description Language. Use the following Scastie Template for testing and questions: https://scastie.scala-lang.org/xrdIdl36SmqFancoEFErAw. | 4 Servers |

| Chisel Lang | 624 Members |

| Discussion about the Chisel Hardware Description Language. Use the following Scastie Template for testing and questions: https://scastie.scala-lang.org/xrdIdl36SmqFancoEFErAw. | 4 Servers |

| Sender | Message | Time |

|---|---|---|

| 19 Mar 2024 | ||

tymcauley (Tynan McAuley) tymcauley (Tynan McAuley) | Not sure you want -DLLVM_TARGETS_TO_BUILD="AArch64" (unless that's your Linux platform), probably want to change AArch64 to host. Were you testing this for macOS AArch64 jackkoenig (Jack Koenig) ? | 18:49:43 |

keithdr93 (keithdr93) keithdr93 (keithdr93) | Thanks jackkoenig (Jack Koenig) I'll try and get around to testing the docker build. That you were able to run firtool and compile a .fir file is encouraging | 20:00:31 |

| 20 Mar 2024 | ||

jackkoenig (Jack Koenig) jackkoenig (Jack Koenig) | * Then you can configure with: | 18:22:20 |

jackkoenig (Jack Koenig) jackkoenig (Jack Koenig) | tymcauley (Tynan McAuley): good catch, indeed you should use host | 18:24:16 |

| 21 Mar 2024 | ||

keithdr93 (keithdr93) keithdr93 (keithdr93) | So this worked for me (I did tweak the build target to X86, and I used But I'm trying to understand why this build works without the version error for | 14:17:50 |

jackkoenig (Jack Koenig) jackkoenig (Jack Koenig) | Alpine Linux ships with Musl libc and then some of the options at the end of the config ensure it gets statically linked | 23:05:05 |

| 22 Mar 2024 | ||

hutch31 (Guy Hutchison) hutch31 (Guy Hutchison) | Late to the thread but ran into the same problem, and ended up using Docker containers | 09:28:48 |

hutch31 (Guy Hutchison) hutch31 (Guy Hutchison) | I created a script that runs firtool inside a docker container: https://github.com/hutch31/chisel-tools-container/blob/main/bin/firtool | 09:29:47 |

hutch31 (Guy Hutchison) hutch31 (Guy Hutchison) | Firtool takes advantage the "automatic logic" feature of SystemVerilog to create intermediate combinatorial signals inside of clocked blocks, for example: While perfectly legal and synthesizable, it appears to drive the Mentor lint/formal tool nuts because it thinks _GEN_11 and _GEN_12 are registers. Is there a way to turn this off so that it explictly creates wires as intermediates? I tried "disallowLocalVariables" and it had no effect on these. | 09:37:02 |

lsteveol (lsteveol) lsteveol (lsteveol) | Redacted or Malformed Event | 12:04:19 |

lsteveol (lsteveol) lsteveol (lsteveol) | hutch31 (Guy Hutchison): can you send out your fir tool command? disallowLocalVariables should have done it | 12:05:26 |

| 29 Mar 2024 | ||

| 04:01:59 | ||

| I want to write some Chisel that should optimise to a some shared buses with some tri-state buffers to select which input goes to which bus. As far as I can tell, Mux1H is the correct choice for this? What is a FixedPoint? Why wouldn't the Mux1H optimisation work well on this? I cannot find anything about FixedPoint in the docs. | 04:06:06 | |

| * | 04:06:21 | |

jackkoenig (Jack Koenig) jackkoenig (Jack Koenig) | Chisel does not represent tri-state buffers so unless your synthesis tool is going to generate them from standard muxing (doubtful but I'm not sure) then that might be a problem for you. | 20:29:43 |

jackkoenig (Jack Koenig) jackkoenig (Jack Koenig) | FixedPoint is a Data-type for representing fixed point numbers. There's not much in the docs because it was removed in Chisel 5.0. I'm not aware of any reason why Mux1H wouldn't work for FixedPoint since the optimizations that Mux1H enables are agnostic to how the bits being muxed are interpreted. | 20:31:00 |

In reply to @jackkoenig-57e1805540f3a6eec0665030:gitter.imAt most, this is going on an FPGA, so there will likely be no internal tri-state logic. Also, it seems strange to me that synthesis would not generate a shallow mux using a shared bus whenever possible. In any case, it's all hypothetical, but it's nice to have an implementation that could at least make use of the optimisation I came up with. | 21:47:03 | |

| For context, it's for spreading accesses across banks in a predictor based on instruction addresess. Instruction addresses in the same cycle are always consecutive, though they vary between 16 and 32 bit (RVC and RVI). This is to reduce the complexity of the predictor storage so that each bank has one write port and two read ports, instead of a unified predictor memory with many n write ports and 2n read ports. | 21:53:37 | |

| * | 21:55:36 | |

jackkoenig (Jack Koenig) jackkoenig (Jack Koenig) | I am not certain, but I don't think shared buses are actually more efficient in modern ASIC technologies. I would have to consult with someone more knowledgable than me about physical design to be sure though. | 21:56:51 |

jackkoenig (Jack Koenig) jackkoenig (Jack Koenig) | You can represent the bus with Analog in Chisel, but for driving it you'll have to use Verilog BlackBoxes | 21:57:23 |

In reply to @jackkoenig-57e1805540f3a6eec0665030:gitter.imhttps://github.com/chipsalliance/chisel/blob/main/docs/src/explanations/muxes-and-input-selection.md This would be the offending file then. Should the documentation perhaps be updated here? | 21:57:48 | |

jackkoenig (Jack Koenig) jackkoenig (Jack Koenig) | I am surprised by that comment but in any case it's moot as FixedPoint has been removed! Thanks for the pointer, I'll remove the reference. | 21:58:58 |

In reply to @jackkoenig-57e1805540f3a6eec0665030:gitter.im Yeah, I'm not that worried about actually implementing it. It's all academic anyway and I can probably hand-wave it away by saying that Mux1H conveys the semantic meaning that I want. | 21:59:53 | |

jackkoenig (Jack Koenig) jackkoenig (Jack Koenig) | Yeah makes sense! I think it should work well enough | 22:01:34 |

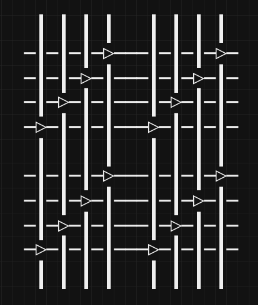

Download image.png | 22:02:22 | |

| I'm surprised by the possibility that tri-state logic wouldn't be the most efficient. I don't see how I'd implement something similar to this without tri-state logic | 22:02:23 | |

| The mux trees would be massive as far as I can tell | 22:03:02 | |

jackkoenig (Jack Koenig) jackkoenig (Jack Koenig) | Let me preface by saying that I am not an expert here and might be wrong, but I do support designers building high-performance stuff in modern technologies and I'm pretty sure they don't use tri-state at all. You are right that the mux trees would be massive (this can be mitigated a bit as most ASIC technologies provide Mux4 primitives which help a little), and the tri-state logic would certainly have fewer wires which helps with routing, but I think you run into drive strength issues with the length of the wire (those tri-state gates have to get pretty big), and the length of time it takes to drive the wire may be just too limiting on your clock speed to make the benefits worth it | 22:05:40 |

jackkoenig (Jack Koenig) jackkoenig (Jack Koenig) | * Let me preface by saying that I am not an expert here and might be wrong, but I do support designers building high-performance stuff in modern technologies and I'm pretty sure they don't use tri-state at all. You are right that the mux trees would be massive (this can be mitigated a bit as most ASIC technologies provide Mux4 primitives which help a little, although that's more with routing than with area), and the tri-state logic would certainly have fewer wires which helps with routing, but I think you run into drive strength issues with the length of the wire (those tri-state gates have to get pretty big), and the length of time it takes to drive the wire may be just too limiting on your clock speed to make the benefits worth it | 22:06:02 |